## D1.3 – PRELIMINARY VERSION OF CPSOSAWARE SYSTEM ARCHITECTURE

Authors Pavlos Kosmides (CTL), Eleni Adamopoulou (CTL)

Work WP1 – Requirements, Use Cases, Specifications and Architecture

Abstract

Package

This document focuses on the capturing and presentation of technical specifications of the system components, including functional and non-functional requirements. It introduces the **CPSoSaware Technical Specification Elicitation Framework**: based on established requirements engineering processes, the framework is aimed at eliciting a comprehensible list of system and component requirements that will facilitate reaching a precise architecture design for the CPSoSaware system. The results from applying the framework are manifested as an aggregate collection of knowledge items related to technical component specifications and requirements that take the form of a **living reference document** accessible by all involved stakeholders, in the sense that it will be frequently revisited and reiterated throughout the project lifetime. The presentation of this living document, along with an account of the defined architectural blocks and the preliminary version of the system architecture, constitute the main outputs from this deliverable.

Funded by the Horizon 2020 Framework Programme of the European Union

## **Deliverable Information**

| Work Package        | WP1 – Requirements, Use Cases, Specifications and Architecture |  |  |  |

|---------------------|----------------------------------------------------------------|--|--|--|

| Task                | T1.3 – CPSoSaware System Specifications and Architecture       |  |  |  |

| Deliverable title   | Preliminary Version of CPSoSaware System Architecture          |  |  |  |

| Dissemination Level | Public                                                         |  |  |  |

| Status              | F                                                              |  |  |  |

| Version Number      | 1.0                                                            |  |  |  |

| Due date            | 31/12/2020                                                     |  |  |  |

# **Project Information**

| Project start and<br>duration | 01/01/2020 – 31/12/2022, 36 months                                                                                                   |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Project Coordinator           | , , ,                                                                                                                                |

|                               | 26504, Rio-Patras, Greece                                                                                                            |

| Partners                      | 1. ATHINA-EREVNITIKO KENTRO KAINOTOMIAS STIS TECHNOLOGIES TIS<br>PLIROFORIAS, TON EPIKOINONION KAI TIS GNOSIS (ISI)<br>* Coordinator |

|                               | 2. FUNDACIO PRIVADA I2CAT, INTERNET I INNOVACIO DIGITAL A CATALUNYA<br>(I2CAT),                                                      |

|                               | 3. IBM ISRAEL - SCIENCE AND TECHNOLOGY LTD (IBM ISRAEL                                                                               |

|                               | 4. ATOS SPAIN SA (ATOS),                                                                                                             |

|                               | 5. PANASONIC AUTOMOTIVE SYSTEMS EUROPE GMBH (PASEU)                                                                                  |

|                               | 6. EIGHT BELLS LTD (8BELLS)                                                                                                          |

|                               | 7. UNIVERSITA DELLA SVIZZERA ITALIANA (USI),                                                                                         |

|                               | 8. TAMPEREEN KORKEAKOULUSAATIO SR (TAU)                                                                                              |

|                               | 9. UNIVERSITY OF PELOPONNESE (UoP)                                                                                                   |

|                               | 10. CATALINK LIMITED (CATALINK)                                                                                                      |

|                               | 11. ROBOTEC.AI SPOLKA Z OGRANICZONA ODPOWIEDZIALNOSCIA (RTC)                                                                         |

|                               | 12. CENTRO RICERCHE FIAT SCPA (CRF)                                                                                                  |

|                               | 13. PANEPISTIMIO PATRON (UPAT)                                                                                                       |

|                               |                                                                                                                                      |

## **Control Sheet**

| VERSION | Date       | SUMMARY OF CHANGES AUTHOR             |     |

|---------|------------|---------------------------------------|-----|

| 0.1     | 09/11/2020 | Document outline created              | CTL |

| 0.2     | 10/11/2020 | v1 of Chapters 2 and 3                | CTL |

| 0.3     | 12/11/2020 | v1 of Chapters 4 and 5                | CTL |

| 0.4     | 13/11/2020 | Added Subsection 4.2                  | CTL |

| 0.5     | 17/11/2020 | Added executive summary and Chapter 6 | CTL |

| 0.6     | 02/12/2020 | Added abstract and Appendix A         | CTL |

| 0.7     | 09/12/2020 | v2 of Chapter 5                       | CTL |

| 0.8     | 15/12/2020 | Internal review                       | CTL |

| 1.0     | 18/12/2020 | Final version submitted to EC         | CTL |

|                  | ΝΑΜΕ                                               |

|------------------|----------------------------------------------------|

| Prepared by      | CTL                                                |

| Reviewed by      | Pekka Jääskeläinen (TAU), Georgios Keramidas (UoP) |

| Authorised<br>by | CTL                                                |

| DATE       | RECIPIENT           |

|------------|---------------------|

| 9/12/2020  | Project Consortium  |

| 18/12/2020 | European Commission |

## **Table of Contents**

| Ez | xecutive Summary                                                                                      | 7   |

|----|-------------------------------------------------------------------------------------------------------|-----|

| 1  | Introduction                                                                                          | 8   |

|    | 1.1 Document Structure                                                                                | 8   |

|    | 1.2 Definitions and Acronyms                                                                          |     |

| 2  | Requirements Elicitation and Analysis - Background                                                    |     |

|    | 2.1 A Broad Definition of Requirements Engineering                                                    |     |

|    | 2.2 Methodologies for Capturing Requirements                                                          |     |

|    | 2.2.1 Document Analysis                                                                               |     |

|    | 2.2.2 Interviews with Stakeholders                                                                    |     |

|    | 2.2.3 Requirement Specification Templates                                                             |     |

|    | 2.2.4 Use Case Analysis                                                                               |     |

|    | 2.3 Requirements Elicitation Objectives in CPSoSaware                                                 |     |

| 3  | CPSoSaware Technical Specification Elicitation Framework                                              |     |

|    | 3.1 Component Specification Templates                                                                 |     |

|    | 3.1.1 Descriptive Component Specification                                                             |     |

|    | 3.1.2 Component Inputs and Outputs                                                                    |     |

|    | 3.1.3 Functional and Non-functional Requirements                                                      |     |

|    | 3.1.4 Deployment and Integration Requirements                                                         |     |

|    | 3.2 Consulting with Stakeholders                                                                      |     |

|    | 3.3 Analysis of Description of Action                                                                 |     |

|    | 3.4 Formalization of Captured Requirements                                                            |     |

| 4  | Presentation of Captured CPSoSaware Specifications                                                    |     |

|    | 4.1 Roles                                                                                             |     |

|    | 4.2 Technical Component Specifications                                                                |     |

|    | 4.2.1 Data Collection Module                                                                          |     |

|    | 4.2.2 Intra-Communication Sim Tool                                                                    |     |

|    | 4.2.3 PoCL-Remote                                                                                     |     |

|    | 4.2.4 Slice Manager                                                                                   |     |

|    | 4.2.5 LightEdge                                                                                       |     |

|    | 4.2.6 Hardware Accelerator IP Cores                                                                   |     |

|    | 4.2.7 Security Accelerators for CPS Security Agents/Sensors                                           |     |

|    | 4.2.8 Model Transformation to OpenCL                                                                  |     |

|    | 4.2.9 Xilinx XRT KPI Monitoring                                                                       |     |

|    | 4.2.10Modelling Orchestration Tool                                                                    |     |

|    | 4.2.11 Visual Localization                                                                            |     |

|    | 4.2.12Deep Multimodal Scene Understanding                                                             |     |

|    | 4.2.13User Behaviour Monitoring<br>4.2.14AI Acceleration                                              |     |

|    | 4.2.14Ai Acceleration<br>4.2.15PoCL-accel                                                             |     |

|    | 4.2.15PoCL-accel                                                                                      |     |

|    |                                                                                                       |     |

|    | <ul><li>4.2.17PathPlanning API</li><li>4.2.18XR Tools for Increasing Situational Awareness</li></ul>  | 36  |

|    |                                                                                                       |     |

|    | <ul><li>4.2.19CPS Layer Security Sensors/Agents</li><li>4.2.20TCE (openasip.org) Soft Cores</li></ul> | .57 |

|    | 4.2.20 ICE (openasip.org) son cores                                                                   |     |

|    | 4.2.21 Opened whapper for marginal if Coles                                                           | .37 |

| 4.2.22HW/SW profiling and analysis based on Vitis Tools                         | 39 |

|---------------------------------------------------------------------------------|----|

| 4.2.23 Architecture Optimization                                                |    |

| 4.2.24Intra-Communication Manager                                               |    |

| 4.2.25 Security Runtime Monitoring                                              |    |

| 4.2.26V2X Simulator                                                             | 44 |

| 4.2.27 Manufacturing Environment Simulation                                     | 45 |

| 4.2.28AV Simulation                                                             | 46 |

| 4.2.29Commissioning of Hardware Components in CPSs                              | 47 |

| 4.2.30HLS based SW to HW Transformation                                         | 49 |

| 4.2.31 Extended Reality lifelong learning tools/Interfaces for integrated CPSoS | 49 |

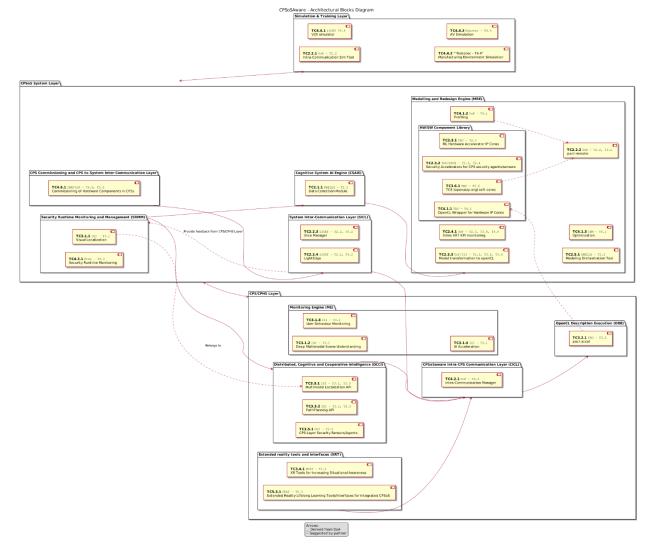

| 5 CPSoSaware System Architecture – Preliminary Version                          | 52 |

| 5.1 Architectural Blocks                                                        |    |

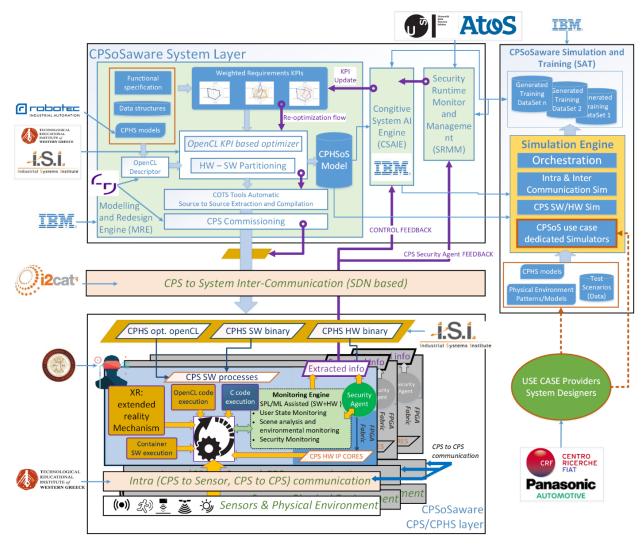

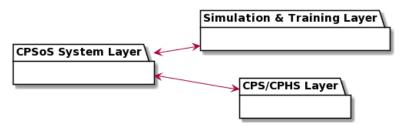

| 5.1.1 CPSoS System Layer                                                        | 53 |

| 5.1.2 CPS/CPHS Layer                                                            | 53 |

| 5.1.3 Simulation and Training Layer                                             | 54 |

| 5.2 Preliminary Architecture Block Diagram                                      |    |

| 6 Conclusions and Next Steps                                                    | 56 |

| References                                                                      |    |

| Appendix A: CPSoSaware Component Specification Template                         | 58 |

## List of Figures

| Figure 1. The process from requirements analysis to system architecture [Liao, 2002]. | 10 |

|---------------------------------------------------------------------------------------|----|

| Figure 2. Top-down vs bottom-up use case analysis approaches [Regnell, 1996].         | 12 |

| Figure 3. CPSoSaware proposed architecture                                            | 52 |

| Figure 4. UML diagram - Architectural blocks                                          | 54 |

| Figure 5. UML diagram - Architectural blocks and sub-blocks                           | 54 |

| Figure 6. UML diagram - Architectural blocks and sub-blocks with technical components | 55 |

|                                                                                       |    |

## List of Tables

Table 1. CPSoSaware compatible roles

19

## **Executive Summary**

This document constitutes D1.3 "Preliminary Version of CPSoSaware System Architecture" and reports on the outcomes of the first phase of Task 1.3 during the first year of the project. The focus is on the technical specifications of the system components, including functional and non-functional requirements. Towards this direction, D1.3 introduces the **CPSoSaware Technical Specification Elicitation Framework**: based on established requirements engineering processes, the framework is aimed at eliciting a comprehensible list of system and component requirements that will facilitate reaching a precise architecture design for the CPSoSaware system. The results from applying the framework are manifested as an aggregate collection of knowledge items related to technical component specifications, requirements, and interfaces that take the form of a **living reference document** accessible by all involved stakeholders, in the sense that it will be frequently revisited and reiterated throughout the project lifetime. The presentation of this living document, along with an account of the defined architectural blocks and the preliminary version of the system architecture, constitute the main outputs from this deliverable.

## **1** Introduction

When referring to software and hardware systems, the term "**architecture**" is used metaphorically, with a meaning equivalent to the architecture of a building, referring to an outline for the system to be developed and the tasks that need to be completed in order to reach the final result [Perry & Wolf, 1992]. Therefore, **system architecture** is aimed at specifying the fundamental components of a (sophisticated) system, the involved software and hardware elements, their interrelations, and the properties of both elements and relations [Clements et al., 2003].

Specifying the architecture of a system is heavily interlinked with the process of **requirements engineering**, which is aimed at assessing whether the developed system meets the purpose for which it was initially intended [Nuseibeh & Easterbrook, 2000]. In fact, the two processes are often seen as complementary: architecture is aimed at the "how", while requirements engineering is aimed at the "what"; both of them, nevertheless, revolve around stakeholder concerns, needs and wishes [Shekaran et al., 1994].

In this context, the overarching goal of this document is to present the technical specifications of the CPSoSaware system components, which have been elicited based on established requirements engineering processes and will lead to deriving a preliminary version of the system architecture.

## **1.1 Document Structure**

The rest of the document is structured as follows:

- **Chapter 2** is an introduction to requirements engineering, requirements elicitation methodologies and the CPSoSaware objectives within this context;

- **Chapter 3** describes the methodologies applied for capturing of CPSoSaware technical component specifications and requirements;

- **Chapter 4** presents the collected knowledge per technical component of the CPSoSaware system;

- **Chapter 5** presents a preliminary version of the CPSoSaware system architecture;

- **Chapter 6** concludes the document with some final remarks and directions for the next steps.

## **1.2** Definitions and Acronyms

Below is a list of the most relevant acronyms used in the document together with their recurring definitions:

| Acronym / Term | Definition                                          |  |  |  |

|----------------|-----------------------------------------------------|--|--|--|

| CICL           | PSoSaware Intra-CPS Communication Layer             |  |  |  |

| CPS            | er-Physical System                                  |  |  |  |

| CPSoS          | yber-Physical System of Systems                     |  |  |  |

| CSAIE          | Cognitive System AI Engine                          |  |  |  |

| DCCI           | Distributed, Cognitive and Cooperative Intelligence |  |  |  |

| DoA  | Grant Agreement No. 871738 – CPSoSAware. Annex 1 Description of the Action. |  |  |  |

|------|-----------------------------------------------------------------------------|--|--|--|

| DSL  | Domain-Specific Language                                                    |  |  |  |

| FPGA | Field-Programmable Gate Array                                               |  |  |  |

| GPU  | Graphics Processing Unit                                                    |  |  |  |

| IP   | Intellectual Property                                                       |  |  |  |

| ME   | Monitoring Engine                                                           |  |  |  |

| ML   | Machine Learning                                                            |  |  |  |

| MRE  | Modelling and Redesign Engine                                               |  |  |  |

| ODE  | OpenCL Description Execution                                                |  |  |  |

| P2P  | Peer to Peer / Point to Point                                               |  |  |  |

| PoCL | Portable Computing Language                                                 |  |  |  |

| RE   | Requirements Engineering                                                    |  |  |  |

| SICL | System Inter-Communication Layer                                            |  |  |  |

| SoC  | System-on-Chip                                                              |  |  |  |

| SRMM | Security Runtime Monitoring and Management                                  |  |  |  |

| SW   | Software                                                                    |  |  |  |

| TRL  | Technology Readiness Level                                                  |  |  |  |

| XRT  | Human in the loop situational awareness using XR tools                      |  |  |  |

## 2 Requirements Elicitation and Analysis - Background

This chapter briefly introduces Requirements Engineering and focuses on two of its key activities, requirements elicitation and analysis. The most popular methodologies for eliciting requirements are then presented, followed by an overview of the objectives of the requirements capturing process within CPSoSaware.

## 2.1 A Broad Definition of Requirements Engineering

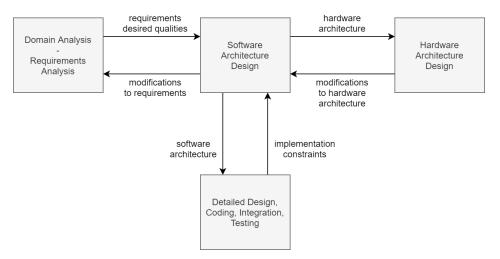

As discussed in the introduction, within the context of software and hardware systems development, **Requirements Engineering (RE)** is the process of assessing whether the developed system meets the purpose for which it was initially intended [Nuseibeh & Easterbrook, 2000]. This process entails the identification of stakeholders and their respective needs from the system, as well as the documentation of these needs in a way that will facilitate their analysis and will drive the subsequent implementation of components that will address them. Due to the numerous challenges involved (e.g., communication gaps with stakeholders, unclear or even conflicting goals and needs, etc.), RE is considered highly critical for delivering an accurate software architecture design and plays a key role particularly during the first steps in the development process, as illustrated in **Figure 1** [Liao, 2002].

Figure 1. The process from requirements analysis to system architecture [Liao, 2002].

RE involves two main activities: (a) **requirements elicitation**, which is aimed at specifying the system to be developed in a form that the end-user understands, and, (b) **requirements analysis**, which promises to deliver an analysis model that can be unambiguously interpreted by the developers of the system [Bruegge & Dutoit, 2009].

Regarding requirements, a typical distinction is often made between **user requirements**, i.e., the requirements derived from the potential end-users, and **technical requirements**, i.e., the requirements referring to the technical aspects of the components to be developed. Although the elicitation of the former usually precedes the latter, a successful system design should involve the collection and analysis of both types of requirements.

More specifically, user requirements typically describe aspects of the system from the end-user perspective that are not directly related to the functional behaviour of the system, like, e.g., response time, accuracy, etc., and are also known as **non-functional requirements**. On the other hand, **functional requirements** specify the explicit functions of a system and its interaction with the environment, and give

an outlook of its technical aspects, processes, and dependencies. Consequently, functional requirements are the key driver in defining the architecture of the system.

In the case of a complex software system consisting of numerous software components, the system requirements include the functional and non-functional requirements of each component, as well as the specifications that refer to the system-wide behaviour and functionality. In order to avoid confusion between the two levels (i.e., system vs component) and to better organize the pertinent knowledge, it is common practice to come up with lists of system and component-level use cases and then map requirements to them accordingly.

## 2.2 Methodologies for Capturing Requirements

During requirements elicitation, it is common practice to apply a variety of related methodologies and techniques, in order to obtain a more holistic outlook of the domain and to acquire knowledge from various stakeholders, such as end-users, domain and technical experts [Eid, 2015]. This subsection briefly presents the most established methodologies in gathering requirements.

## 2.2.1 Document Analysis

The analysis of existing documentation is a valuable first step in requirements elicitation, since it leads to a better understanding of the domain and the system to be developed and can help substantially during the next steps, e.g., for formulating more accurate questions for the interviews with stakeholders (see next subsection). And, inversely, if certain responses from the interviews are unclear, analysing existing documentation may help in clarifying things. The downsides to this approach are that (a) it is a timeconsuming process, and, (b) the documentation may be out of date.

#### 2.2.2 Interviews with Stakeholders

There are two types of interviews with stakeholders in order to elicit requirements: one-on-one sessions and group interviews. One-on-one sessions are arguably the most common technique for gathering requirements and should be well-prepared beforehand, in order to get the most out of them. The appropriate stakeholders to be interviewed should be identified and a list of both open-ended and close-ended questions must be prepared. The former questions facilitate retrieving more holistic and high-level knowledge and allow the interviewer to focus on more specific aspects with more elaborate subsequent questions, while the latter are more useful in covering more topics in a deeper manner and in less time. Once the list of questions is complete, it is typically a good practice to send them to the interviewee prior to the interview so that they better prepare (see also next subsection). An additional good practice is to record the session (with the interviewee's consent), so that the responses can be revisited at a later time.

Group interviews, on the other hand, are similar to one-on-one interviews, with the exception that more persons are being interviewed at the same time. This type of interview is ideal when the interviewees all have similar positions in the organization and/or experience and background. The key advantage of group interviews is that responses by one interviewee may trigger further discussion by the others, which leads to eliciting richer information during the interview. The major drawback is that group interviews are hard to schedule, since establishing a date/time slot that works well for all parties can prove quite challenging.

## 2.2.3 Requirement Specification Templates

Requirement specification templates are structured questionnaires circulated to stakeholders prior to interviews and are very well suited for involving multiple parties at once, guiding them to provide focused

responses and descriptions on specific aspects of the system to be developed. In case of unclear responses, clarifications may be discussed during the interviews.

In the literature one can find several established requirement specification templates, like, e.g., Volere<sup>1</sup>, which can be extended, in order to include additional fields specific to the system at hand.

## 2.2.4 Use Case Analysis

Use cases in software engineering are the sets of actions or events that define the interactions between a system and the involved agents; the latter being human or machines external to the system [Bruegge & Dutoit, 2009]. Use cases do not directly point to requirements, but analysing them leads to identifying desired system behaviours and qualities, which may be implicitly converted to requirements. In the cases of complex systems consisting of multiple components, use cases are typically defined per component or per group of components, and their analysis will lead to extracting functional and non-functional requirements at the component level.

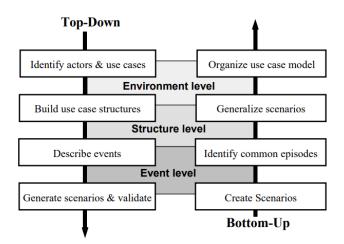

Figure 2. Top-down vs bottom-up use case analysis approaches [Regnell, 1996].

According to Regnell (1996), the process of extracting requirements from use cases can be either bottomup, with the aggregation of component-level use cases comprising the system-level use cases, or topdown, where high-level use cases and related actors are initially identified, and then sub-scenarios and requirements are specified towards the component-level (see **Figure 2**).

## 2.3 Requirements Elicitation Objectives in CPSoSaware

Our overarching objective for the requirements elicitation process during this first period (M1-M12) of the project was focused on generating a project-wide reference document collaboratively with the rest of the involved partners that will focus on the following:

- (a) **Functional and non-functional requirements** both on the component and the system level, identifying the desired functionalities of each component and of the system as a whole.

- (b) Mapping of use cases and roles to the technical requirements.

- (c) **Dependencies** per system component.

<sup>&</sup>lt;sup>1</sup> <u>https://www.volere.org/templates/volere-requirements-specification-template/</u>

#### (d) Potential implications and conflicts between requirements.

Towards this objective, we adopted the requirements elicitation methodologies presented in the previous subsection and came up with a reference document, which we intend to have in the form of a "**living document**" that will be frequently revisited and reiterated. This way, the requirements will be refined and re-adjusted throughout the project's lifecycle. The first version of the document and its elements is described in the rest of this deliverable, while the next iterations of the document will be reported in the upcoming deliverables D1.4 "Second Version of CPSoSaware System Architecture" (due M24) and D1.5 "Final CPSoSaware System Architecture" (due M36).

## **3** CPSoSaware Technical Specification Elicitation Framework

Within CPSoSaware and under the scope of WP1, a task force has undertaken the application of established requirement engineering processes towards fulfilling the requirement elicitation objectives and enabling a precise architecture design for the CPSoSaware system. This chapter is aimed at presenting the activities that were performed to capture technical component specifications, driven by the team's expertise and methodologies found in literature.

## **3.1 Component Specification Templates**

Inspired by the Volere methodology and its variations (see Subsection 2.2.3), a detailed requirement specification template was assembled and distributed to partners involved in the design and implementation of technical components. The template intended to provide a common vocabulary for the homogeneous expression of technical and non-technical details. Divided into four logical sections, the template incorporated free text fields for questions regarding the component high-level description, expected inputs and outputs, functional and non-functional requirements, and deployment/integration conditions.

Since this effort started early in the project and proceeded in parallel with the definition of pilot use cases, the participants were encouraged to only insert available information - omitting fields that remained yet undecided - and periodically revisit the document with updates deriving from the evolvement of system-level requirements.

A detailed presentation of the template segments is presented in the following sections. The complete specification template can be found in *Appendix A: CPSoSaware Component Specification Template*.

## 3.1.1 Descriptive Component Specification

The first part of the component specification template intended to capture high-level component metadata. More specifically, it included the following fields:

- **Task name:** The task(s) from the Description of Action (DoA) where the component implementation is detailed.

- **Task leader:** The partner(s) assigned to lead the corresponding task(s) in the DoA.

- **Component name:** The name of the technical component.

- **Type:** An indication whether the component is a software, a hardware, or a combination of both.

- **Short description:** An abstract of the component's functionality and purpose within CPSoSaware.

- **Methodologies that will be used:** A short description of the technical and/or scientific methodologies orchestrated for the component implementation.

- User-defined scenarios (non-technical): A set of component-level use case descriptions in a non-technical manner.

- **Map to project objectives:** An association of the technical component with the CPSoSaware project objectives as described in the DoA.

- **Relevant Use Cases:** An association of the technical component with the CPSoSaware pilot use cases.

• Estimated date of first release that can be deployed/integrated: An early estimation for the first delivery expressed as the month of the project's lifecycle.

## 3.1.2 Component Inputs and Outputs

A template section is dedicated to collecting information regarding a component's interfaces and expected inputs/outputs. Along with the headway in the pilot use case definitions, the acquisition of such knowledge will prove critical for the design of meaningful pipelines for the CPSoSaware system. A mapping between data owners and data consumers is expected to facilitate development and integration. The corresponding questionnaire fields for data inputs are:

- **Main inputs:** A description of the expected input sources for this component.

- **Input data from partner:** The partner(s) responsible for providing the input(s), either via their technical components or in the form of datasets, etc.

- **Nature of expected input:** The expected format for the requested input (e.g. JSON format, video streams, image files, etc.).

- **Related Scenarios:** Use case scenarios and pilots that associate with the production and/or processing of these data.

- **Interfaces:** The interface(s) provided or required by the technical component for the retrieval of input data.

- **Triggered by:** The event(s) or condition(s) that will trigger the execution or functionality of the component.

Similarly, the fields for expected outputs are:

- **Main outputs:** A description of the output(s) that will be produced by this component.

- **Output data to partner:** The partner(s) responsible for consuming the generated output(s), either via their technical components or in the form of datasets, etc.

- **Nature of expected output:** The expected format for the produced output (e.g., JSON format, video streams, image files, etc.).

- **Related Scenarios:** Use case scenarios and pilots that associate with the consumption and/or processing of these data.

- Interfaces: The interface(s) provided or required by the technical component for the delivery of output data.

## 3.1.3 Functional and Non-functional Requirements

The definition of requirements at the technical component level is meant to portray functional and nonfunctional necessities for the design, operation, and integration of the component itself. This bottom-up approach suggests that the collection of requirements per component will constitute a subset of the system-level requirement set. Consequently, this effort will be associated with the top-down definition of requirements at the pilot use case level, reported in the upcoming D1.2 "Requirements and Use Cases". Therefore, the corresponding fields in the template are:

• **Main functional requirements:** A set of technical requirements for the design, development, and functioning of the component.

• **Main non-functional requirements:** A set of qualitative and quantitative conditions that the component should cover. These can be related with topics such as scalability, security, accessibility, availability and more.

## 3.1.4 Deployment and Integration Requirements

The final section of the component specification template aims at eliciting technical details related to the development, deployment, and integration with the rest of the CPSoSaware system. More specifically, the included fields are:

- **Development environment:** The development environment incorporates the operating system(s), IDE(s) and programming language(s) used for the implementation of the component.

- **Execution time:** An estimation for processing time of the component, in case of including heavy processing tasks, etc.

- **Execution frequency:** This indicates how often the execution is expected to take place, in case of periodic executions.

- **Software requirements:** The component's dependency from external software.

- Hardware requirements: The component's dependency from external hardware.

- **Communications:** Connectivity requirements, such as access to the Internet, Bluetooth interface, etc.

- **Integration requirements:** Specific requirements regarding the integration of the component with the rest of the system.

- **Deployment requirements:** Specific requirements regarding the deployment of the component.

- Security requirements: Specific requirements to avoid any potential security issues.

- **Privacy requirements:** Specific requirements to avoid any potential privacy issues.

- **Critical factors:** Any critical factors that might affect the development or functionality of the component.

- **Containerization:** The ability to be containerized (e.g. with Docker) if the component of discourse is a software module.

#### 3.2 Consulting with Stakeholders

Extensive discussions with involved technology experts allowed the extraction of requirements, system specifications, and potential architecture designs. A series of project meetings, periodic WP1 meetings, ad-hoc sessions with stakeholders and offline communications enabled the dissemination of the component specification templates, the collection of the component list, the elicitation of useful information and, finally, the establishment of a common understanding on the overall CPSoSaware system design. Recurring communications also ensured better comprehension over the applied requirements elicitation framework and allowed the iteration of the process towards a more precise requirement elaboration.

## 3.3 Analysis of Description of Action

The requirements elicitation process at the early stages of the project demanded the detailed study and analysis of the main reference document, the DoA. The detailed descriptions of the overall project objectives, the proposed system architecture, and the use cases offer a playground for the extraction of functional and non-functional requirements. Work package and task descriptions extensively portray the expected technical components and features. As a result, details from the document were initially studied to identify the main architectural blocks and sub-blocks, while the use case analysis resulted in a preliminary requirement set. Since the DoA was authored prior to the project kick-off, the knowledge derived from the document acted as the basis for the requirements elicitation process, and needed to be verified, refined, and extended along with the maturing of the project's objectives.

## **3.4 Formalization of Captured Requirements**

A critical part of the requirements engineering process is requirement management. This includes the mechanisms for documenting, prioritizing, tracking, agreeing, and communicating specifications to relevant stakeholders. Therefore, we have pursued the aggregation of collected knowledge related to technical component specifications and requirements into a single living document, accessible by all involved stakeholders, where information is encoded in a uniform format. This document intends to limit ambiguity and facilitate the reference and update of requirements throughout the project lifetime.

The document is in MS Excel format, containing several tables that are briefly described below. Information is encoded using appropriate prefixes/suffixes and colour codes to facilitate browsing and search.

#### Technical component list

This table includes the collection of CPSoSaware technical components, along with short descriptions, architectural blocks, state-of-the-art, and requirements. More specifically, the table contains the following columns:

- **Code:** A unique identifier assigned to the technical component, by assembling the prefix *TC*, the task number, and an incrementing integer (e.g., *TC3.1.2*). This field also acts as a hyperlink to the component specification template previously filled by the corresponding technology expert, in order to enable the fast review of provided information.

- **Component name:** The name of the technical component.

- **Type:** Indicates whether this is a software, hardware, or both.

- **Task:** Indicates the task(s) involved in the design and implementation of the component.

- **Partner:** The partner(s) leading the design and implementation of the component.

- Short description: A textual description of the scope, functionality, and objectives of the component.

- Architectural block: A set of architectural blocks and sub-blocks has been identified by the study of DoA (see Section 0). This field allows the selection from a pre-defined list of values [CPSoS system layer, CPS/CPHs layer, Simulation and training]. This classification of components enables the conceptualization of the architecture.

- Architectural sub-block: Similarly, the component is assigned to the appropriate sub-block. The list of sub-blocks also derives from the DoA analysis and conferencing with stakeholders.

- **Functional requirements:** A set of technical/functional requirements that characterize the component as a standalone module. The requirements are encoded using the component's code, along with the suffix *.R* and an incrementing integer (e.g. *TC3.1.2.R2*) to enable unambiguous references to requirements.

- **Non-functional requirements:** Just like above, non-functional requirements are listed and encoded using the suffix *.NFR* and an incrementing integer (e.g. *TC3.1.2.NFR1*).

- **State-of-the-Art / Innovation:** A short textual description for the state-of-the-art in the technological domain of the technical component, along with potential innovation and advance beyond the state-of-the-art.

- **Current TRL:** The technology readiness level of the component.

#### Use cases list

This table enlists the identified use cases at the component level (see Section 2.2.4). Use cases are expressed with the simple pattern <u>Actor -> interacts (Use case or functionality) -> Component</u>. The table contains the following columns:

- **Component code:** A reference to the technical component using its unique identifier.

- **Component name:** The name of the technical component.

- Use cases: The set of use cases for this technical component. Each use case is assigned a code combining the component code with the suffix \_UC and an incrementing integer (e.g. TC3.1.2\_UC1).

- Actor: The entity that interacts with the component within the context of the specific use case. An actor, which assumes a *role*, can be a human that interfaces with the component or another software/hardware. System-compatible roles are extensively described on a dedicated table.

- If Actor is HW/SW, identify: If the actor interacting with the use case has been defined as some hardware or software component, it should be denoted here which external or system component that is. The corresponding component code is the required value (e.g. *TC3.1.1*). This is meant to facilitate the precise architecture definition. In several cases, an actor's appropriate use case code is also defined in this field, indicating connections like: *The use case of component TC3.1.1 (TC3.1.1\_UC1) will interact with the use case of component TC3.1.2 (TC3.1.2\_UC2)*. The expected result of this drill is to generate sequences of interconnected use cases which will be later used for the definition of sequence diagrams and system-level use cases.

- **Role's interaction:** A textual description of the interaction between the actor and the component within the context of this use case.

#### **Roles list**

This is a table for listing actor types (roles), and - in case of human roles - their responsibilities, rights, and duties towards the system.

## 4 Presentation of Captured CPSoSaware Specifications

This section presents the knowledge captured via the application of the specification elicitation framework described in Sections 2 and 3. This knowledge is contained in the *living document*, arranged in structures, as presented in Section 3.4.

## 4.1 Roles

As already mentioned, *roles* indicate the types of actors that interact with the CPSoSaware system and its technical **components**. These actors may be other system components, external systems or humans participating in use cases. The identification of the CPSoSaware-compatible roles, along with their potential interactions with CPSoSaware, is crucial for the definition of precise use cases and meaningful architecture designs. Defining roles is a continuous process, highly affected by the ongoing design of pilot use cases, therefore it is performed on an iterative basis. Table 1 presents the currently defined actor types.

| Actor                                                                                      | Interaction                                                                                                 |  |  |  |  |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Analyst                                                                                    | Uses data-driven processes to gain insights about required actions potential improvements                   |  |  |  |  |

| CPS/CPSoS Designer Designs the models for CPSs/CPSoS simulations, communicated deployment. |                                                                                                             |  |  |  |  |

| End-user                                                                                   | Provides specifications, requirements and preferences for the modelling and system design of CPSs and CPSoS |  |  |  |  |

| HW/SW component                                                                            | -                                                                                                           |  |  |  |  |

#### Table 1. CPSoSaware compatible roles

## 4.2 Technical Component Specifications

This section outlines the specifications for the technical components provided by the responsible partners who filled in the respective information in the shared reference document. The information was then homogenized into a uniform format by lead partner CTL and is presented subsequently per component.

## 4.2.1 Data Collection Module

The Data Collection Module is the component based on ElasticSearch that will be developed in order to ingest, store and manage data that is obtained from the activities in T2.1 covering the analysis of user skills/factors, virtual cognitive user/environment models and metrics modelling.

| <b>Code:</b> TC2.1.1 | <b>Task:</b> T2.1 | Partner: 8Bells          |  | Type: Software | <b>TRL:</b> 2 |

|----------------------|-------------------|--------------------------|--|----------------|---------------|

| Architectural block: |                   | Architectural sub-block: |  |                |               |

| CPSoS system layer                                                                                                                                                                                                                               |                                                 |               | Cogni | itive System AI Engine (CSAIE)                                                                                                                                                               |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| State-of-the-Art / Innovation:<br>Still unclear if a well-known tool will be used. For the first step of the questionnaires, we can use google forms                                                                                             |                                                 |               |       |                                                                                                                                                                                              |  |  |

| in order to collect the data from the pilots and then we will study the way to store them, analyse and graphically represent the outputs (e.g., ElasticSearch Kibana is considered)                                                              |                                                 |               |       |                                                                                                                                                                                              |  |  |

| Functional requiren                                                                                                                                                                                                                              | nents                                           |               | Non-  | functional requirements                                                                                                                                                                      |  |  |

|                                                                                                                                                                                                                                                  | vents list to register e                        |               |       | <b>.1.NFR1</b> The DCM should scale automatically to the demand of new DCM metric data.                                                                                                      |  |  |

|                                                                                                                                                                                                                                                  | o demonstrate in gra<br>can be initially desigr |               | TC2.1 | .1.NFR2 The DCM should provide a secure ng of The metrics data.                                                                                                                              |  |  |

| TC2.1.1.R3 Use stati variables.                                                                                                                                                                                                                  | stics to track importa                          | nt changes in |       |                                                                                                                                                                                              |  |  |

| TC2.1.1.R4 Should p                                                                                                                                                                                                                              | provide library of hum                          | an metrics.   |       |                                                                                                                                                                                              |  |  |

| TC2.1.1.R5 Should b way these metric.                                                                                                                                                                                                            | e able to display in a g                        | graphical     |       |                                                                                                                                                                                              |  |  |

| TC2.1.1.R6 The open<br>Data Collection data                                                                                                                                                                                                      | rator should be able to<br>metrics.             | o query the   |       |                                                                                                                                                                                              |  |  |

| TC2.1.1.R7 The open from a CSV/Spreads                                                                                                                                                                                                           | rator will be able to in<br>heet into the DCM.  | put data      |       |                                                                                                                                                                                              |  |  |

| <ul> <li>TC2.1.1.R8 The system shall ensure the confidentiality and integrity of the data being transmitted in the system.</li> <li>TC2.1.1.R9 The system shall ensure the availability of its services to the relevant stakeholders.</li> </ul> |                                                 | d in the      |       |                                                                                                                                                                                              |  |  |

| Component-level U                                                                                                                                                                                                                                | se Cases                                        |               |       |                                                                                                                                                                                              |  |  |

| Name                                                                                                                                                                                                                                             | Actor type                                      | Actor (SW/H   | W)    | Interaction                                                                                                                                                                                  |  |  |

| TC2.1.1_UC1                                                                                                                                                                                                                                      | Analyst                                         |               |       | Collects and stores end-user requirements and preferences (skills, gender, expertise with ICTs,                                                                                              |  |  |

| Store end-user specifications                                                                                                                                                                                                                    | End-user                                        |               |       | health condition, daily routines, etc) via<br>surveys, interviews, group sessions, etc.                                                                                                      |  |  |

| TC2.1.1_UC2<br>Analyse end-user<br>specifications                                                                                                                                                                                                | Analyst<br>End-user                             |               |       | Models users by analysing activities,<br>behavioural parameters, etc, by retrieving<br>stored knowledge. Specifies the number and<br>type of users to be involved in each pilot use<br>case. |  |  |

## 4.2.2 Intra-Communication Sim Tool

Tool designed and implemented to match network requirements imposed by the application and deployed CPSoS to proposed network technologies and configurations (e.g., modulation, signal strength,

duty cycle etc.) and network topologies. The tool will be based on the NS3 simulator and it will be built based on experimentation on models of dominant wireless protocols for intra-communication, e.g., BLE, ZigBee/802.15.4, Wi-Fi.

| <b>Code:</b> TC2.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>Task:</b> T2.2     | Partner: L                                      | JoP                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                               | Type: Software                   | <b>TRL:</b> 4     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------|

| Architectural block:<br>Simulation and training                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |                                                 | Archited                                                                                                                                                                                                                                                                                                                                                                                                                  | Architectural sub-block:                                                                                      |                                  |                   |

| State-of-the-Art / In<br>We are not aware of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | able to deliver       | r the NS3 simulator through a well-defined API. |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |                                  |                   |

| Functional requirem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nents                 |                                                 | Non-fur                                                                                                                                                                                                                                                                                                                                                                                                                   | ncti                                                                                                          | onal requirements                |                   |

| <ul> <li>TC2.2.1.R1 The user should be able to feed the simulator with specific network scenario configuration.</li> <li>TC2.2.1.R2 The tool will be able to record the simulation results in log files.</li> <li>TC2.2.1.R3 The tool will be able to process the log files and extract the evaluation results of the simulation.</li> <li>TC2.2.1.R4 The simulation outcomes will be able to be indexed in database and visualized (e.g. Prometheus/Grafana, Elasticsearch/Kibana)</li> <li>TC2.2.1.R5 The evaluation results will be formulated and fed back to the input of the tool to perform optimizations through iterations.</li> </ul> |                       |                                                 | <ul> <li>TC2.2.1.NFR1 The tool should be able to scale according to the load.</li> <li>TC2.2.1.NFR2 Adoption of microservices paradigm (e.g. containerization).</li> <li>TC2.2.1.NFR2 Authentication/authorization schemes will be supported.</li> <li>TC2.2.1.NFR3 The tool will expose well-defined APIs to allow third-party services to integrate</li> <li>TC2.2.1.NFR4 The tool will be available online.</li> </ul> |                                                                                                               |                                  |                   |

| Component-level Us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | se Cases              |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |                                  |                   |

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Actor type            | Actor (if SW/                                   | /HW) II                                                                                                                                                                                                                                                                                                                                                                                                                   | nte                                                                                                           | raction                          |                   |

| TC2.2.1_UC1<br>Define network<br>requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CPS/CPSoS<br>Designer |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           | Defines and models p<br>parameters.                                                                           |                                  | rmance and energy |

| TC2.2.1_UC2<br>Simulate network<br>topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CPS/CPSoS<br>Designer |                                                 | t                                                                                                                                                                                                                                                                                                                                                                                                                         | Simulates various network technologies,<br>topologies and configurations based on de<br>network requirements. |                                  | •                 |

| TC2.2.1_UC3<br>Generate<br>proposed network<br>technologies and<br>optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPS/CPSoS<br>Designer |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               | ieves the proposed neigurations. | etwork            |

## 4.2.3 PoCL-Remote

Scalable distributed OpenCL runtime layer with P2P event synchronization capabilities.

| <b>Code:</b> TC2.2.2                                                                                                                                                                                                                                     | <b>Task:</b> T2.2     | Partner: T    | AU                                                                                                                                                                                                     | Type: Software                                                                                                                                              | <b>TRL:</b> 3 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|

| Architectural block:<br>CPSoS system layer                                                                                                                                                                                                               |                       |               |                                                                                                                                                                                                        | Architectural sub-blocks:<br>CPSoSaware Modelling and Redesign Engine (MRE)<br>CPS Commissioning and CPS to System Inter-<br>Communication Layer components |               |  |  |

| State-of-the-Art / Innovation:<br>Previous similar projects did not focus on low latency aspects of CPS or edge offloading.                                                                                                                              |                       |               |                                                                                                                                                                                                        |                                                                                                                                                             |               |  |  |

| Functional requirem                                                                                                                                                                                                                                      | ents                  |               | Non-fui                                                                                                                                                                                                | nctional requirements                                                                                                                                       |               |  |  |

| <ul> <li>TC2.2.2.R1 Provide access to all OpenCL-supported devices in a network distributed platform from a single host application.</li> <li>TC2.2.2.R2 Support peer-to-per synchronization of devices without host-application round trips.</li> </ul> |                       |               | <ul> <li>TC2.2.2.NFR1 At most 15% overhead in latency on top of the unavoidable network latencies.</li> <li>TC2.2.2.NFR2 Can utilize 80% of the theoretical bandwidth for buffer transfers.</li> </ul> |                                                                                                                                                             |               |  |  |

| Component-level Us                                                                                                                                                                                                                                       | e Cases               |               |                                                                                                                                                                                                        |                                                                                                                                                             |               |  |  |

| Name                                                                                                                                                                                                                                                     | Actor type            | Actor (if SW/ | /HW) I                                                                                                                                                                                                 | nteraction                                                                                                                                                  |               |  |  |

| <b>TC2.2.2_UC1</b><br>Configure the<br>OpenCL runtime<br>layer                                                                                                                                                                                           | CPS/CPSoS<br>Designer |               |                                                                                                                                                                                                        | Configures the paramete<br>OpenCL runtime environ                                                                                                           | -             |  |  |